- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-SDRAM/DDR2 (Altera)IP DDR2 SDRAM CONTROLLER

�� �

�

�

�3–32�

�Chapter� 3:� Functional� Description�

�Parameters�

�Memory�

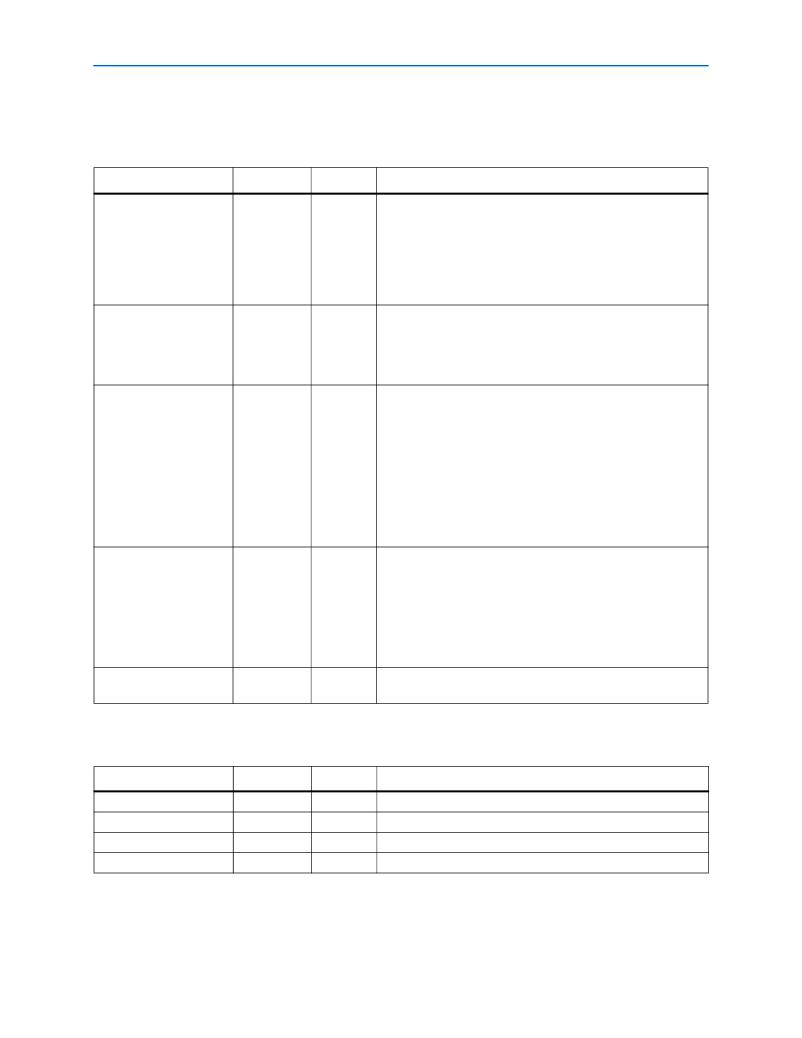

��Table� 3–11.� Memory� Interface� Parameters�

�Parameter�

�Data� bus� width�

�Value�

�≥� 8�

�Units�

�Bits�

�Description�

�The� width� of� your� DDR� or� DDR2� SDRAM� data� interface.� Your� local�

�interface� is� twice� the� width� of� the� memory� interface.� This� value�

�depends� on:�

�■�

�■�

�■�

�The� memory�

�Bandwidth� requirement�

�Number� of� DDIO� pins� available� on� the� selected� FPGA� device�

�Number� of� chip� selects�

�1,� 2,� 4,� or� 8�

�—�

�The� number� of� chip� selects� in� your� memory� interface.� This� is�

�equivalent� to� the� depth� of� your� memory� in� terms� of� number� of�

�chips.� This� value� depends� on� the� type� of� memory� DIMM� selected.�

�If� there� are� two� DIMMs� and� the� memory� modules� on� both� DIMMs�

�have� two� ranks,� the� number� of� chip� selects� is� 4.�

�Number� of� chip� selects�

�per� DIMM�

�1� or� 2�

�—�

�The� number� of� chip� selects� on� each� DIMM� in� your� memory�

�system.� This� option� is� completely� dependent� on� the� type� of�

�external� SDRAM� that� you� are� using.� SDRAMs� may� come� in� two�

�memory� chips� (called� rank)� connected� in� parallel,� with� only� a�

�unique� chip� enable� signal.� This� configuration� allows� the� two� ranks�

�to� share� address� and� data� lines.� Selectively� asserting� only� one�

�chip� enable� signal� at� a� time,� allows� twice� the� memory� depth�

�compared� with� only� a� single� chip.�

�If� there� are� two� memory� chips� in� the� memory� module,� select� 2,�

�otherwise� select� 1.�

�Use� dedicated� PLL�

�outputs�

�On� or� off�

�—�

�Turn� on� to� use� dedicated� PLL� outputs� to� generate� the� clocks,�

�which� is� recommended� for� HardCopy� II� devices.�

�HardCopy� II� designs� use� dedicated� PLL� outputs� for� noise�

�immunity,� better� signal� integrity,� and� minimal� variation� over�

�process,� temperature,� and� voltage.�

�When� turned� off,� the� ALTDDIO� megafunction� generates� the� clock�

�outputs.�

�Number� of� clock� pairs�

�from� FPGA� to� memory�

�1� to� 6�

�—�

�The� number� of� differential� clock� pairs� driven� from� the� FPGA� to� the�

�memory.� More� clock� pairs� reduce� the� loading� of� each� output.�

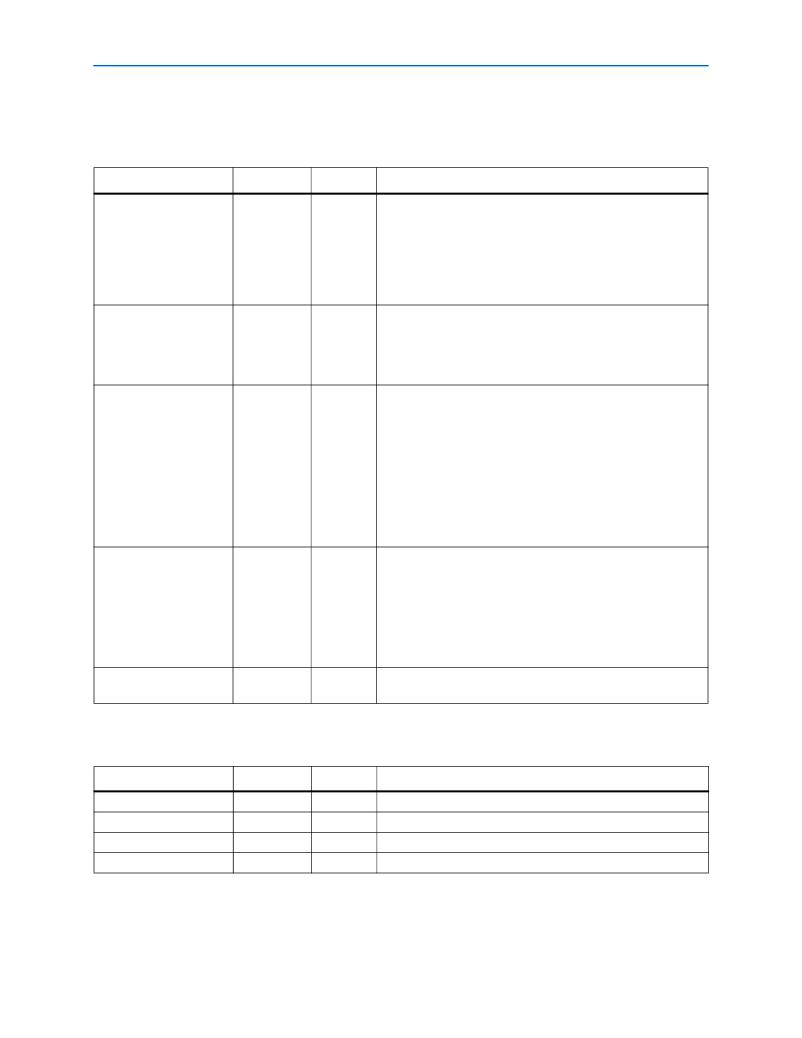

��Table� 3–12.� Memory� Property� Parameters� (Part� 1� of� 2)�

��Parameter�

�Row� address� bits�

�Column� address� bits�

�Bank� address� bits�

�Precharge� address� bit�

�Range�

�10� to� 14�

�8� to� 13�

�2� or� 3�

�8� or� 10�

�Units�

�Bits�

�Bits�

�Bits�

�–�

�Description�

�The� number� of� row� address� bits� for� your� memory.�

�The� number� of� column� address� bits� for� your� memory.�

�The� number� of� bank� address� bits� for� your� memory.�

�The� address� bit� to� use� as� the� precharge� pin.�

��?� March� 2009� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-SLITE2

IP SERIALLITE II

IP-SRAM/QDRII

IP QDRII SRAM CONTROLLER

IP-VITERBI/SS

IP VITERBI LOW-SPEED

IP4220CZ6,125

IC USB DUAL ESD PROTECT 6TSOP

IPA-66-1-600-10.0-A-01-T

CIRC BRKR 10A 2POLE SCREW TERM

IPR-CSC

IP COLOR SPACE CONVERTER RENEW

IPR-ED8B10B

IP 8B10B ENCODER/DECODER RENEW

IPS-VIDEO

IP VIDEO/IMAGE PROCESSING SUITE

相关代理商/技术参数

IP-SDRAM/DDR3

功能描述:开发软件 DDR3 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR

功能描述:开发软件 DDR SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/LPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPSE.4.33SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.33SM600 GLASS FIBER (MIN ORDER 50)

IPSE.4.62SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.62SM600 GLASS FIBER (MIN ORDER 50)

IPS-EMBEDDED

功能描述:开发软件 Embedded IP Suite MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPS-EVAL-EH-01

功能描述:ENERGY HARVESTING BOARD RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:THINERGY® 标准包装:1 系列:- 主要目的:数字电位器 嵌入式:- 已用 IC / 零件:AD5258 主要属性:- 次要属性:- 已供物品:板 相关产品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP